HDMI1.4协议阅读笔记

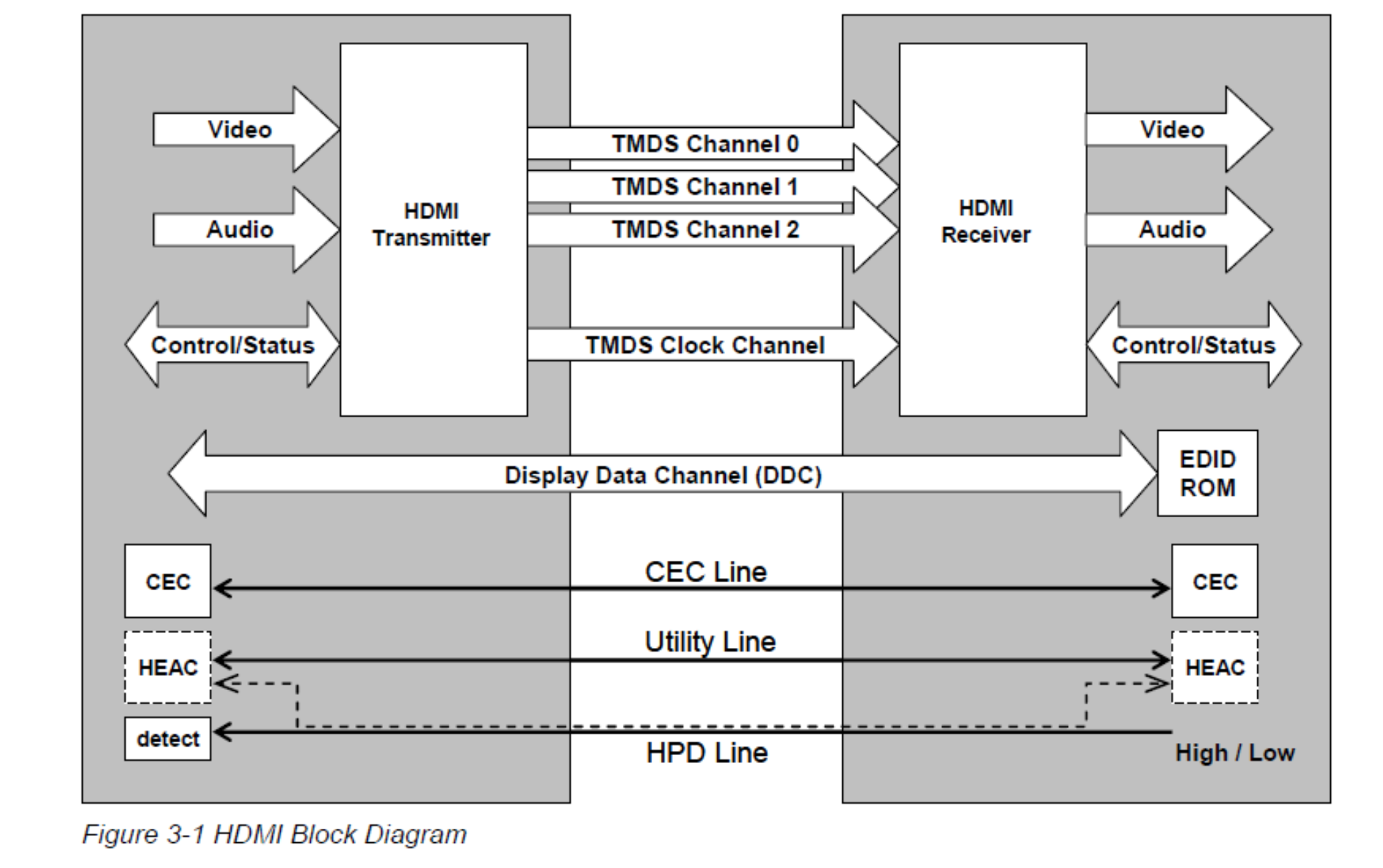

HDMI传输系统综述

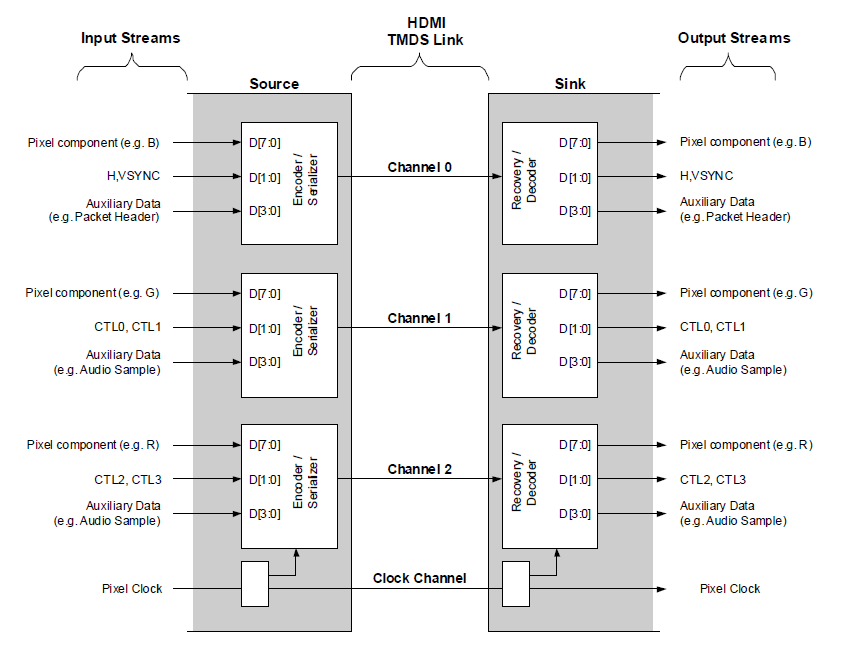

一个 HDMI 传输系统由发送端(Source)和接收端(Sink)组成,线缆中主要包含:

- 四个差分对组成的主数据链路:三个 TMDS 数据通道 + 一个 TMDS 时钟通道

- VESA DDC(I²C),用于显示参数的配置与状态读取

- CEC(可选),消费电子控制总线

- HEAC,用于音频回传和以太网信号

- HPD,热插拔检测

本文聚焦在 HDMI1.4 的数据链路层――也就是 TMDS 链路在行场时序中的组织与编码方式。

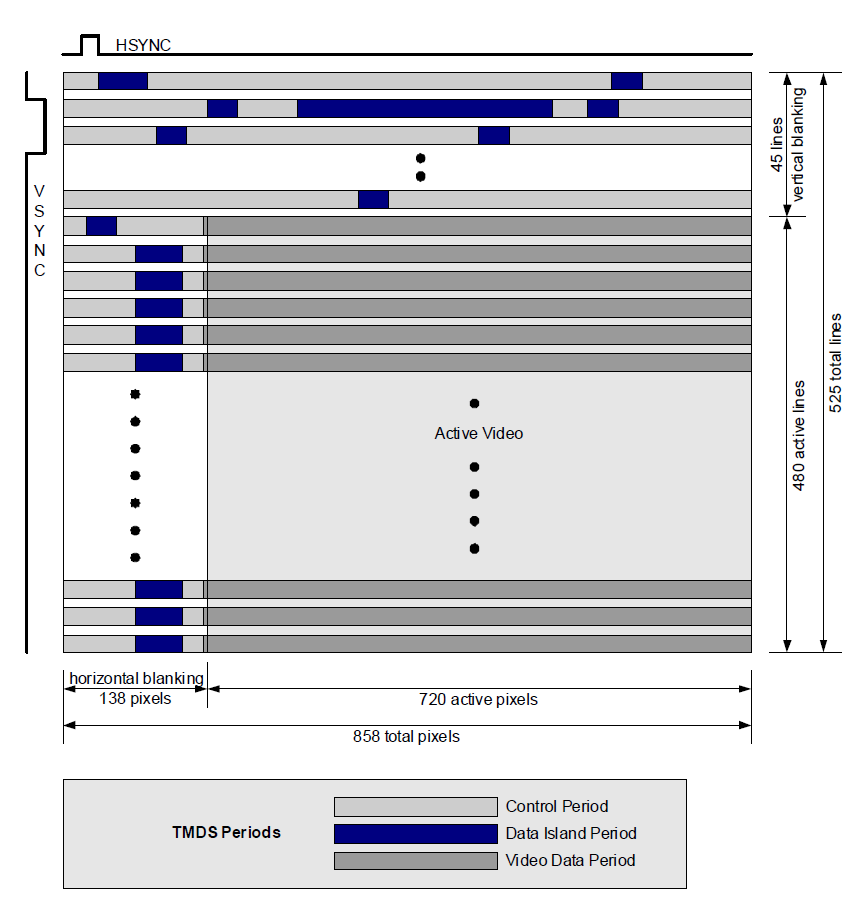

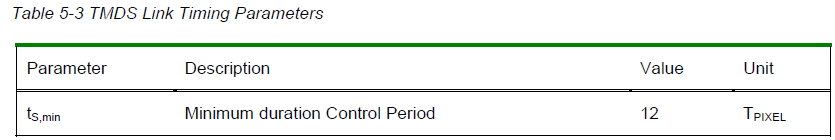

TMDS链路与时序总览

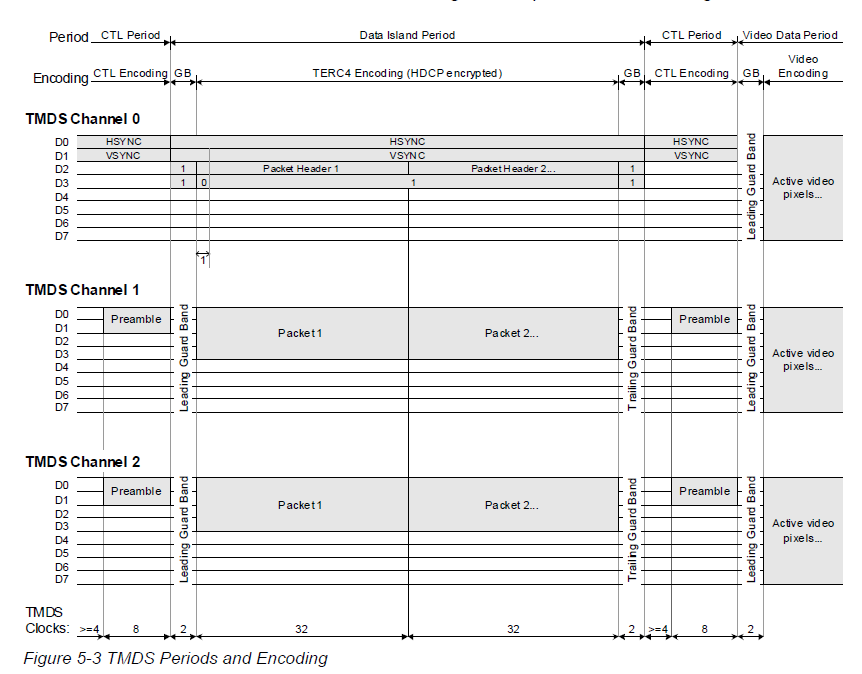

一帧视频在 TMDS 链路上会被拆分为三个传输区段:

- Control Period:承上启下,告知即将到来的数据类型,并携带 HSYNC/VSYNC。

- Data Island Period:传输音频样本与各种 InfoFrame 辅助数据。

- Video Data Period:传输有效像素数据。

同步信号 HSYNC/VSYNC 在特定行、列被拉起,用于 Source 与 Sink 的帧时序对齐。实际线上传输的帧尺寸大于有效分辨率(例如 720×480p),因为在行首、行尾及场间插入了 blank 区域(包含 HBlank 与 VBlank)。这些 blank 区由 Control Period 与 Data Island Period 交替填充,而真正显示在屏幕上的区域被称为 active 区,即 Video Data Period。

TMDS 时钟与编码粒度

在 TMDS clock 通道的每一次跳变(一个 TMDS Clock)中,每条数据通道都会输出一个 10bit 的字符。不同类型的数据使用不同的编码:

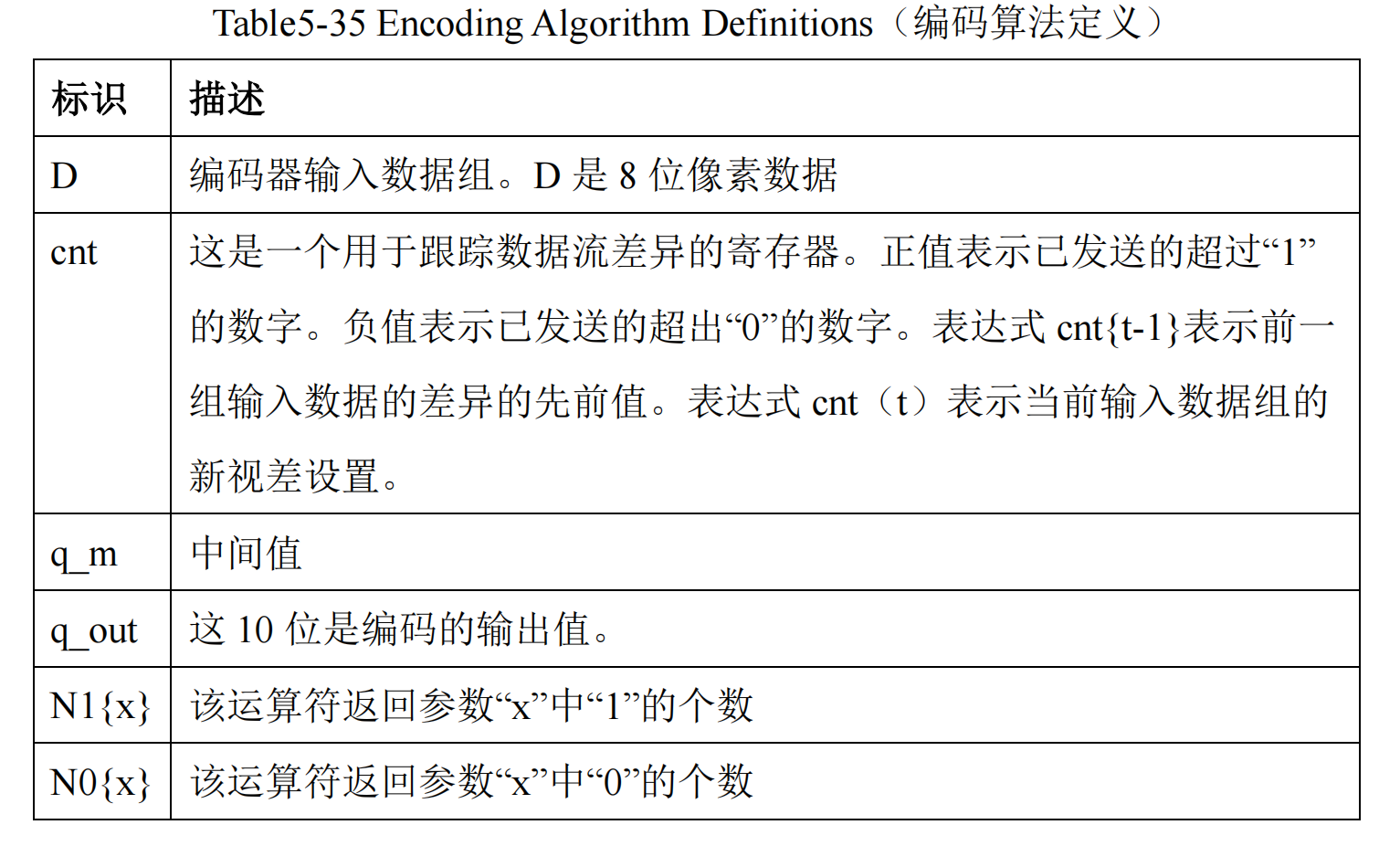

| 数据类型 | 原始位宽 | 编码方式 | 输出位宽 |

|---|---|---|---|

| Control data | 2 bit | 控制字符编码 | 10 bit |

| Packet data | 4 bit | TERC4 编码 | 10 bit |

| Video data | 8 bit | TMDS 8b/10b 编码 | 10 bit |

| Guard Band | - | 固定控制字符 | 10 bit |

因此“每个 TMDS Clock / 每条数据通道始终 10bit”这条规则贯穿整个链路,只是编码方式会跟随传输期而变化。

与 DVI 的兼容关系

HDMI 的 TMDS 物理层本质沿袭自 DVI,因此只要把 Data Island 功能关闭,HDMI 发送端就能向传统 DVI 显示器输出:

- DVI 仅存在 Control Period + Video Data Period,blank 区由 DE=0 触发,控制字符只携带 HSYNC/VSYNC;

- HDMI 在空白期新增 Data Island Period,把原先 DVI 的 C0

C3 扩展为 CTL0CTL3,用来插入音频、InfoFrame; - 两者的像素 TMDS 编码流程完全一致,Guard Band、Preamble 这类结构只在 HDMI 才会出现。

所以理解 DVI 可以帮助我们把握 HDMI“Control→数据岛→视频”的节奏,也方便在需要与 DVI 屏兼容时裁剪掉 Data Island。

Control Period:承上启下

Control Period 是 HDMI 链路的“呼吸区”,它在 Video 与 Data Island 之间填充,用于:

- 传输 HSYNC / VSYNC(Channel0)

- 告知接下来是 Video 还是 Data Island(Channel1/2 上的 CTL0~CTL3)

- 提供字符同步、HDCP EESS 等控制信息

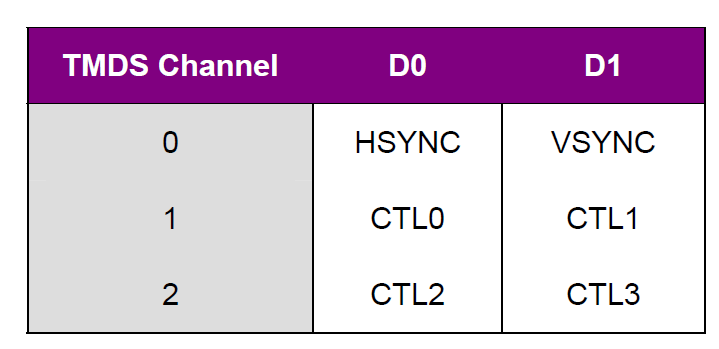

| 通道 | 承载内容 |

|---|---|

| Channel 0 | HSYNC、VSYNC |

| Channel 1 | CTL0、CTL1 |

| Channel 2 | CTL2、CTL3 |

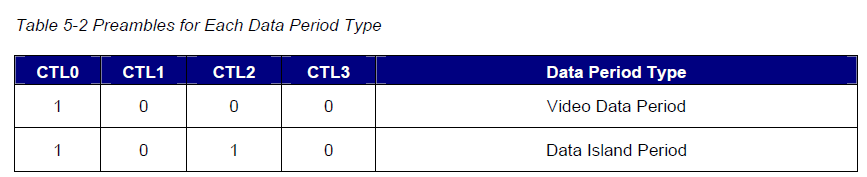

Preamble:判定下一个周期

每个数据周期开始前都会插入长度为 8 个 TMDS Clock 的 Preamble,全部由相同的控制字符构成,用于提示下一阶段的类型。

在 Preamble 期间 HSYNC、VSYNC 按原行场节奏继续输出,而 CTL0~CTL3 组合被限定为如下两种合法取值:

| CTL0 | CTL1 | CTL2 | CTL3 | 意义 |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 下一个周期是 Video Data Period |

| 1 | 0 | 1 | 0 | 下一个周期是 Data Island Period |

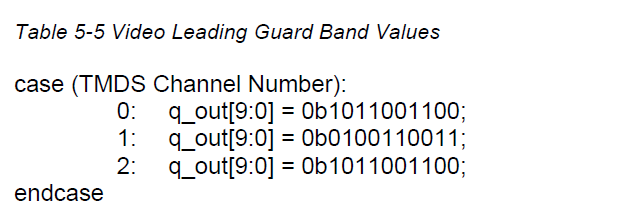

Guard Band:真正的数据边界

Preamble 结束后紧接着会发送 Guard Band――两个特殊的 TMDS 字符,用以标记数据区的真实起点,同时告知 Sink 接下来到底是 Video 还是 Data Island。

- Video Guard Band 只出现在 Video Data Period 的起始位置

- Data Island Guard Band 位于 Data Island Period 的首尾(Leading/Trailing,均为 2 个 TMDS Clock)

Preamble 用于“宣布类型”,Guard Band 用于“宣布开始”。

协议规定 CTL=1010 的控制字符只允许出现在 Preamble 中,否则接收端可能误以为 Data Island 即将到来。

Character Synchronization

- TMDS character 指编码后的 10bit 单元。Video/Data Island 字符的跳变很少,而 Control 字符往往包含 >=5 次跳变。

- Source 必须让每次 Control Period 至少持续 2 个 TMDS Clock,让 Sink 可以凭借跳变密度确认字符边界。

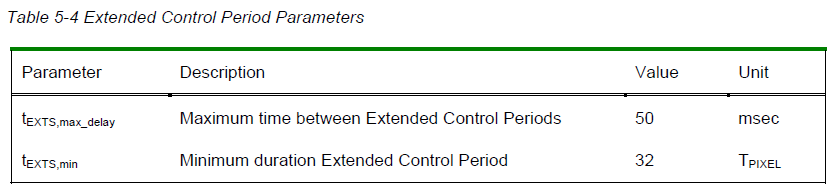

- Source 还需至少每 50ms 插入一次持续 32 个 TMDS Clock 的 Extended Control Period,以便进一步稳固同步。

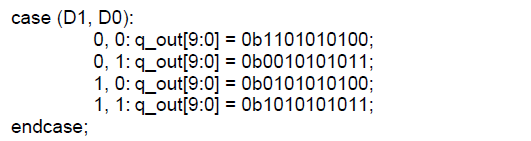

Control Period Encoding

Control Period 使用固定表格完成 2bit→10bit 的编码,编码形式示意如下:

Data Island Period:音频与辅助数据

Data Island Period 不承载像素,而是负责所有 Packet 数据(如 Audio Sample、AVI/Vendor InfoFrame 等)。其组织规则如下:

- 前置 8 个 TMDS Clock 的 Data Island Preamble

- Leading / Trailing Guard Band 各 2 个 TMDS Clock

- 核心数据区由 1~8 个 Packet 组成(每个 Packet 固定 32 个 TMDS Clock)

- Preamble 之前必须有 ≥4 个 TMDS Clock 的普通 Control Period,保证字符同步

- Data Island 与 Video 周期间必须插入至少一个 Control Period,二者不可直接相邻

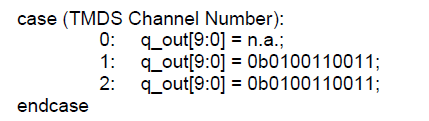

Guard Band 期间的通道分工

在 Data Island Guard Band 内:

- Channel1/Channel2 被直接映射为固定的 10bit 字符(如下图所示)

- Channel0 中 D2/D3 固定为 1;根据 HSYNC/VSYNC 不同,会出现 0xC~0xF 四种 nibble,再经 TERC4 编码得到最终字符

与此同时:

- Channel0 的 D0、D1 仍承担 HSYNC、VSYNC

- Leading Guard Band 之后的第一个 TMDS Clock,Channel0 的 D3 置 0,其余时刻保持 1

- Channel1/Channel2 的 8bit 数据负责 Packet 内容(Guard Band 内除外)

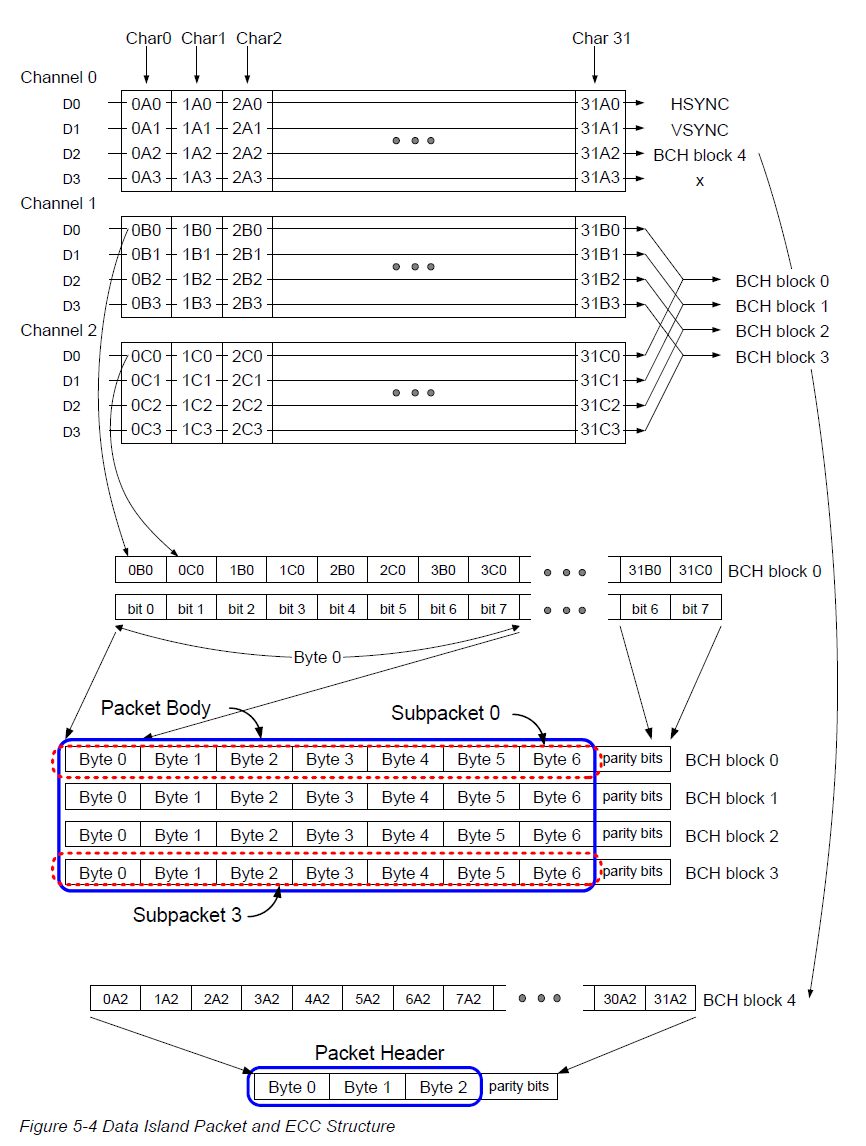

Packet 结构

每个 Packet = Header + Body,两部分都配有 BCH 校验位:

- Packet Header(HB0/HB1/HB2)

- 原始 24bit 数据 + BCH(32,24) → 32bit

- 由 Channel0 的 D2 传输

- Packet Body(4 个 Subpacket)

- 每个 Subpacket:56bit 数据 + BCH(64,56) → 64bit

- 共 4 个 Subpacket(Block0~Block3),通过 Channel1/Channel2 传输

Subpacket 会被线性映射为 PB0~PB27:

| Subpacket | 包含字节 | 映射到 PB |

|---|---|---|

| Subpacket0 | SB0~SB6 | PB0~PB6 |

| Subpacket1 | SB0~SB6 | PB7~PB13 |

| Subpacket2 | SB0~SB6 | PB14~PB20 |

| Subpacket3 | SB0~SB6 | PB21~PB27 |

这种连续映射便于 Sink 逐字节解析 Packet Body,也满足 BCH Block 的数据布局要求。

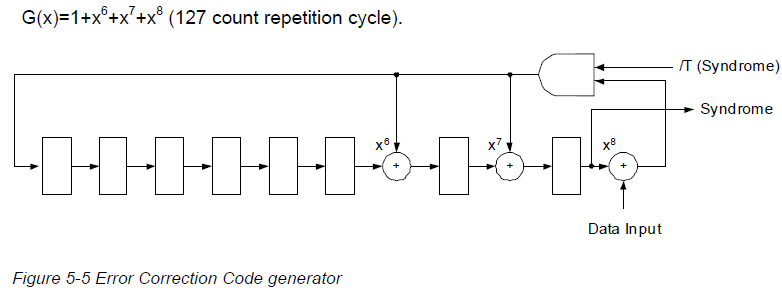

BCH 纠错

HDMI 通过 BCH 编码保证音频与 InfoFrame 数据的可靠性:

- Subpacket 使用 BCH(64,56)

- Packet Header 使用 BCH(32,24)

下图给出了各字段的 BCH 位置分布,具体多项式略。

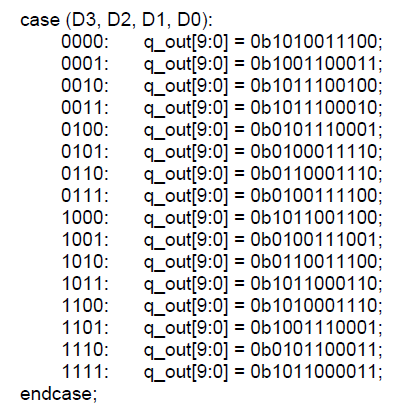

Data Island 的编码:TERC4

Data Island 所有 4bit 数据(Guard Band、Preamble、Packet 内容)都必须先过 TERC4 编码,再映射到 10bit TMDS 字符。

1 | Data Island |

Video Data Period:像素传输

Video Data Period 是 TMDS 链路真正搬运 RGB 像素的阶段:

- Video Preamble(8 个 TMDS Clock) + Video Guard Band(2 个 TMDS Clock,仅出现在段首)

- Active Video 区域三条通道分别传输 Blue/Green/Red 的 8bit 数据

- 三条通道共完成一个像素的 24bit 传输,TMDS Clock = Pixel Clock

- 在 InfoFrame 中还会声明具体像素格式、色域等信息

消隐区 (Blank) 的 control 信号

一行像素结束后进入 HBlank/VBlank,此时链路回落到 Control Period。最常见的“纯消隐”状态如下:

- Channel0 的 2bit 控制字段分别携带 HSYNC、VSYNC,其电平随行/场位置切换;

- Channel1/Channel2 的 CTL0~CTL3 统一置 0000,等价于 DVI 的 DE=0,表示“当前没有有效像素、也没有 Data Island”;

- 如果需要在 blank 内插入音频或 InfoFrame,则在

0000之后发送 CTL=1010 的 Data Island Preamble,再接 Guard Band 与 Packet。

因此,Video 消隐区的控制组合可以理解为 “HSYNC/VSYNC = 实际同步状态 + CTL0~CTL3 = 0000”,只有当要进入 Data Island 时才会被新的 CTL 组合取代。

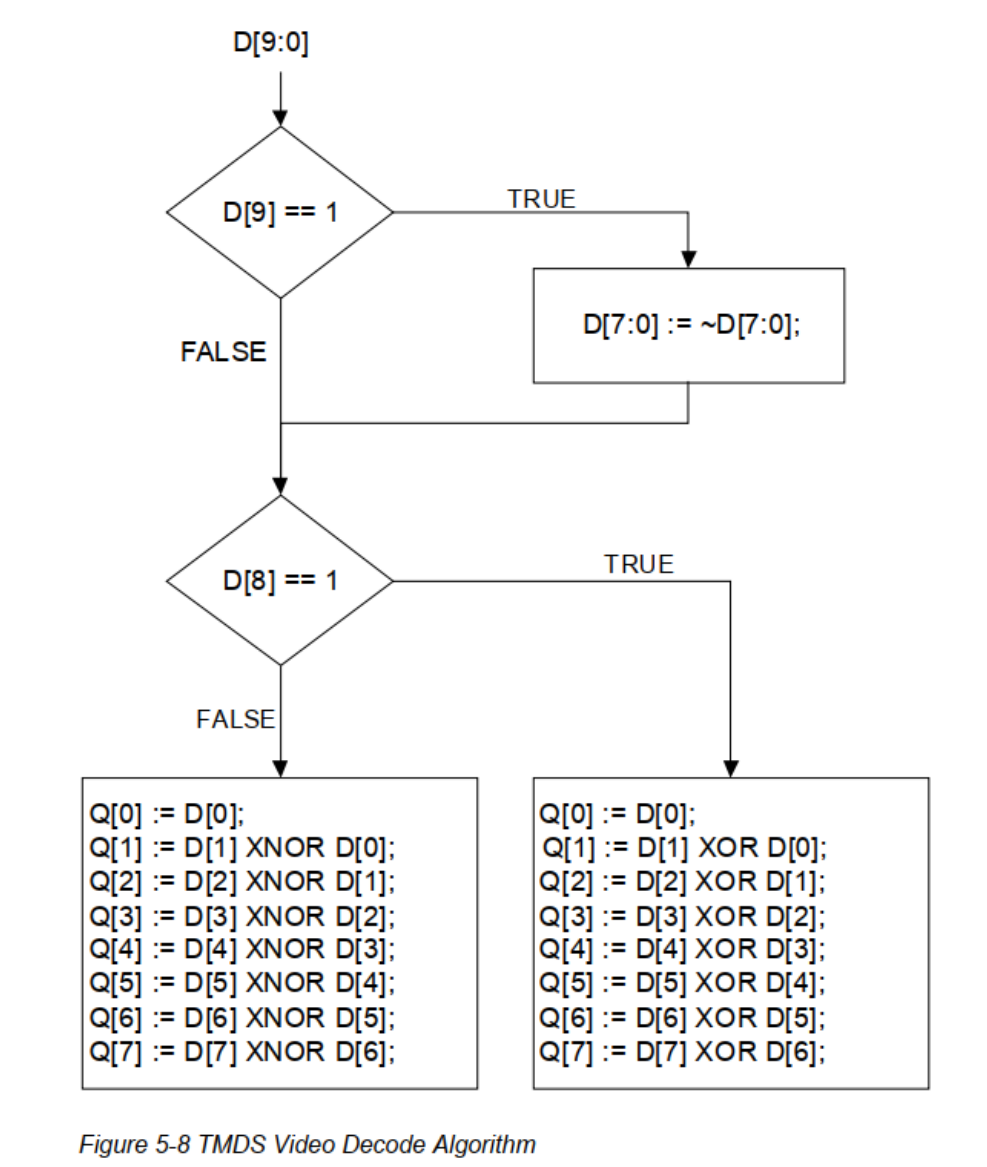

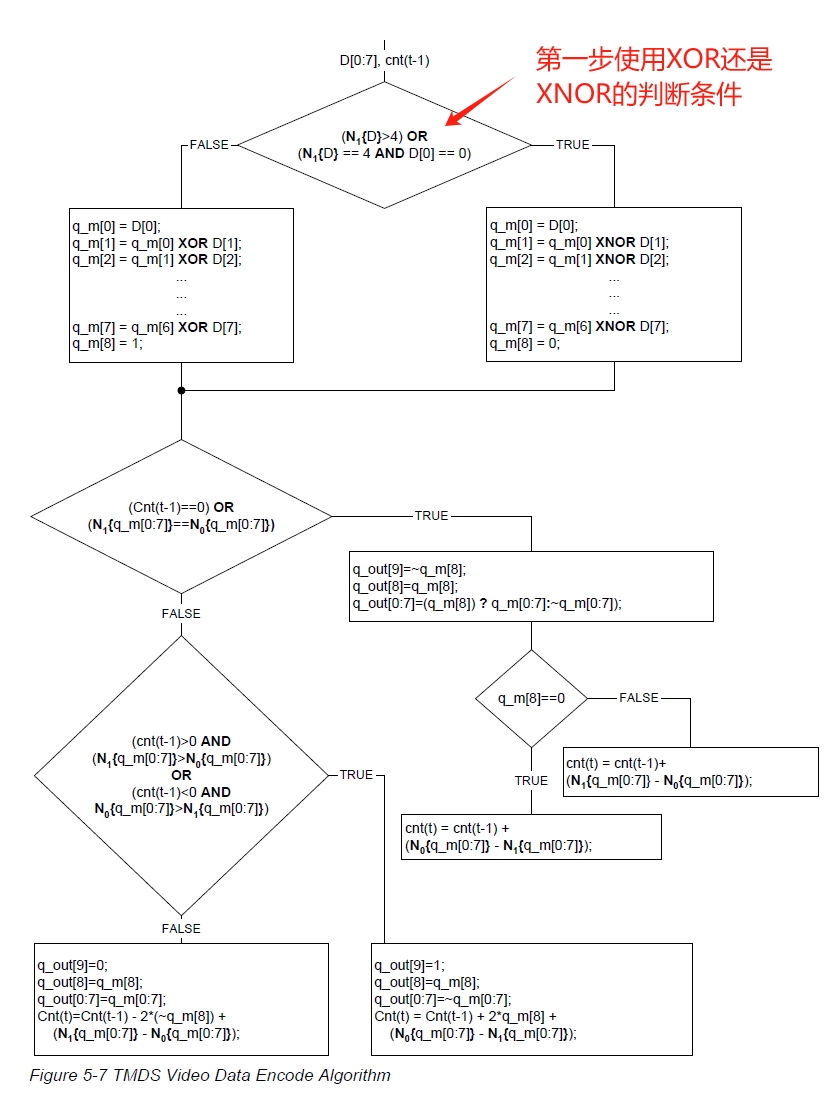

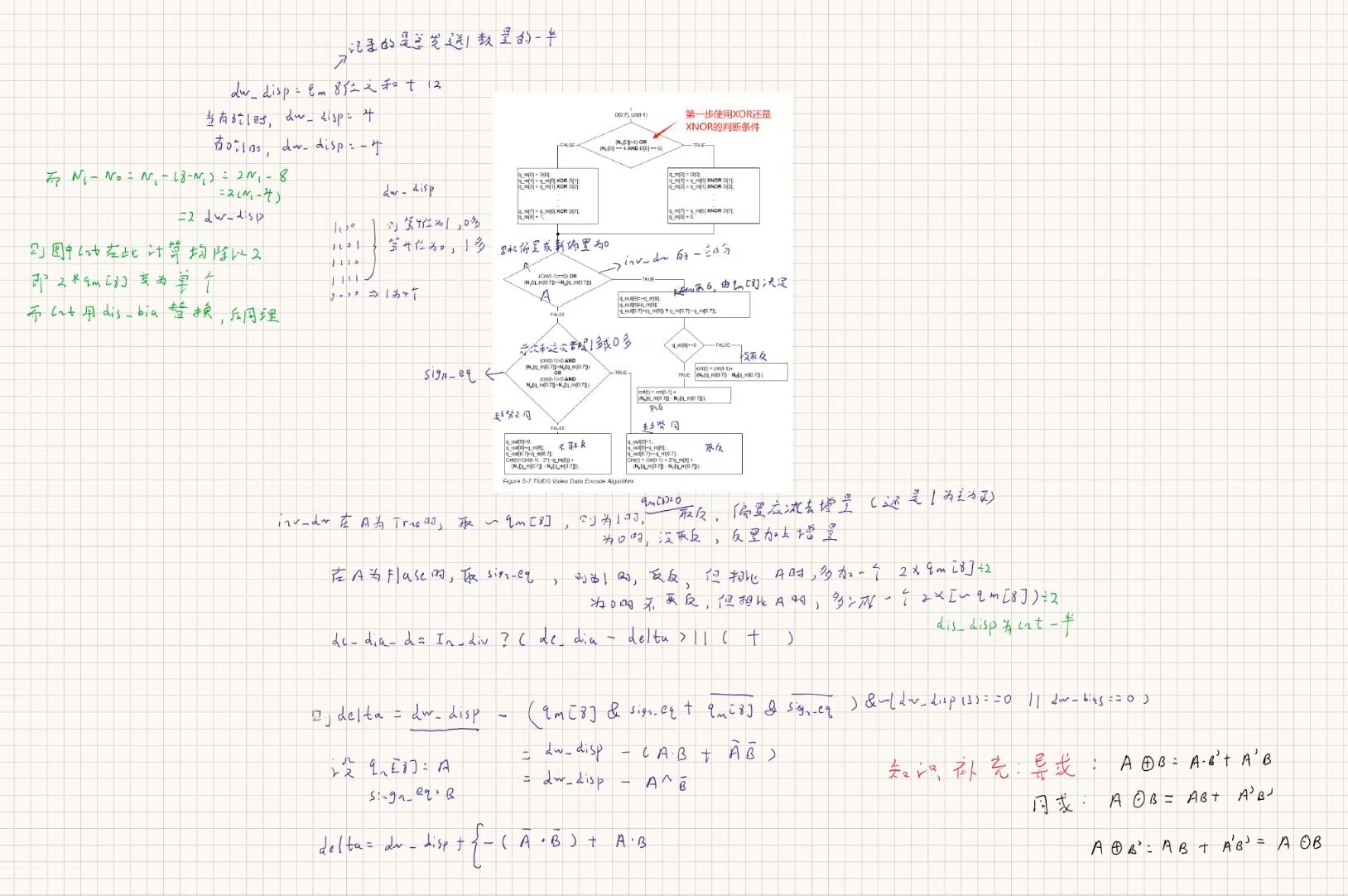

TMDS 编码流程(8bit→10bit)

TMDS(Transition Minimized Differential Signaling)的目标是减少跳变和保持直流平衡,整个过程可拆为两步:

Step 1:8bit→9bit(最小化跳变)

编码器会分别尝试 XOR 与 XNOR 两种方式递推 8bit 数据:

- output[0] 直接等于输入 LSB。

- 对 n=1~7,计算

output[n] = input[n] XOR output[n-1](或 XNOR 版本)。 - 比较两套结果的跳变次数,选择跳变更少的那套。

- 生成的 9bit 中,MSB 用来标记选择的是 XOR(0)还是 XNOR(1)。

示例:

1 | input = 1100_1010 |

Step 2:9bit→10bit(直流平衡)

第二步为了实现 DC Balance,会增加第 10bit(通常记为 q_m[9]),并根据“已发送 1/0 的累积差值”决定是否将前 9bit 取反。

- 如果当前字符 1 比 0 多且累积差值也偏正,则取反

- 如果累积差与当前字符趋势相反,则保持不变

- 第 10bit 记录此次是否进行了取反

完整流程如下图所示,该编码总共会产出 460 种合法的 10bit 字符。只要编码器运作正常,Video Data Period 中不会出现其他字符;Guard Band、Control Period、Data Island 则各自使用专用字符集合,Sink 可以据此区分当前所处的 Period。

编码方式速查

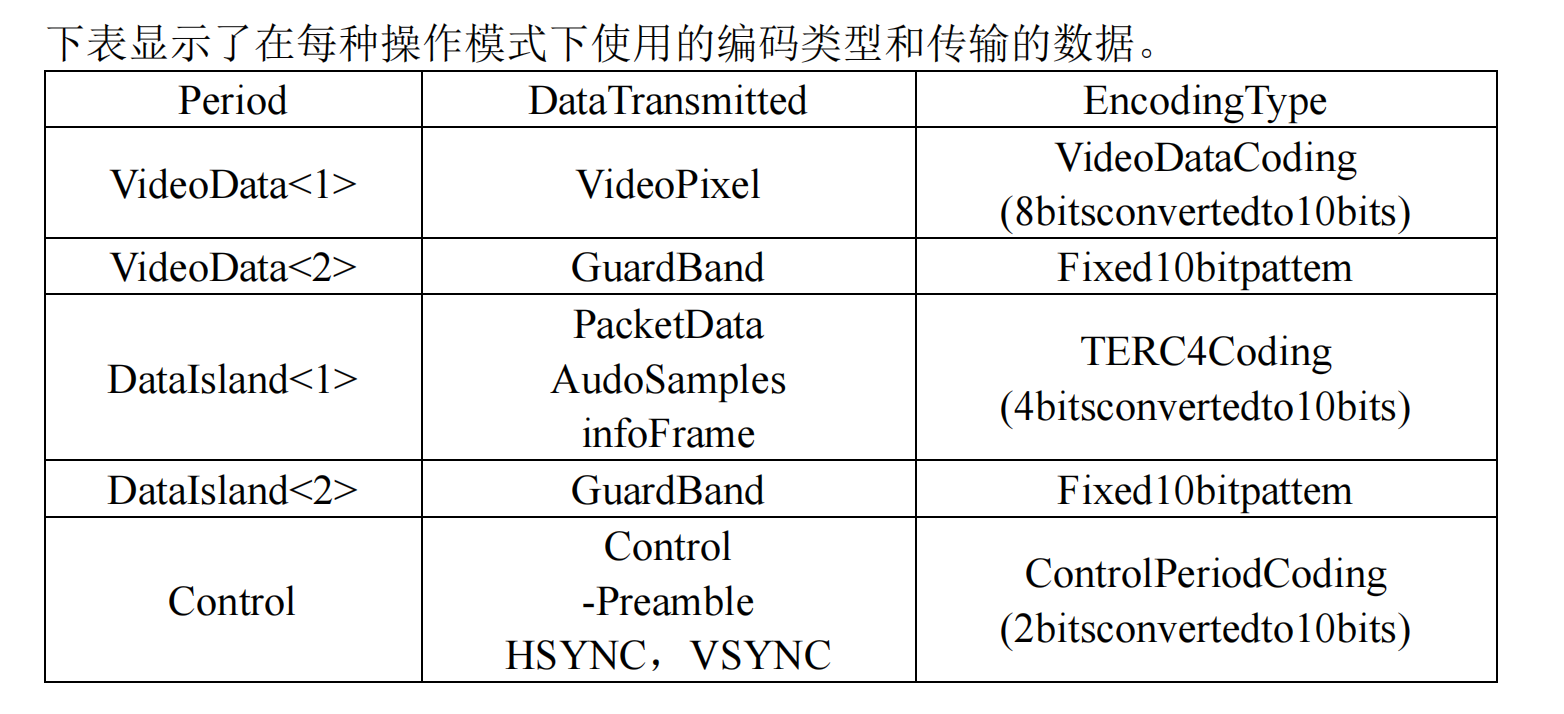

| 场景 | 触发条件 | Guard Band | 编码方式 |

|---|---|---|---|

| Control Period | Video/Data Island 之间的空档 | 固定控制字符 | 2bit→10bit 控制编码 |

| Data Island | Blank 区承载音频/InfoFrame | Leading+Trailing(各 2 个 Clock) | TERC4(4bit→10bit) |

| Video Data | Active 区像素传输 | 仅 Leading(2 个 Clock) | TMDS(8bit→10bit) |

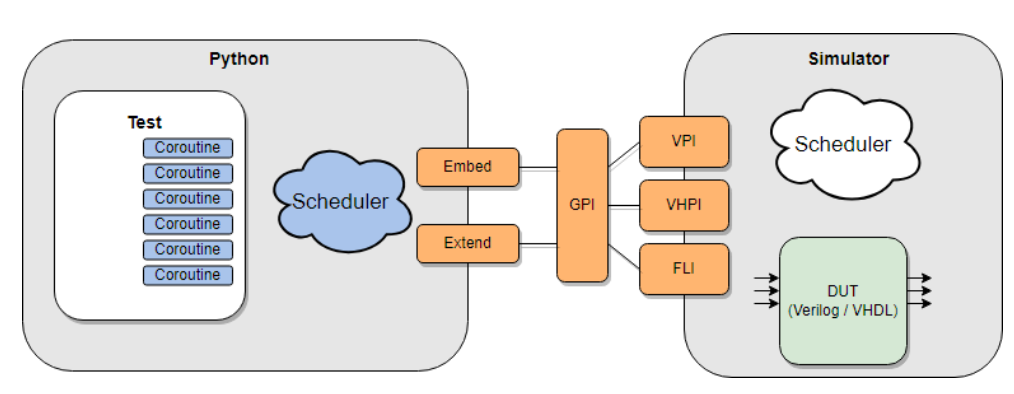

代码设计图

解码方式速查